Hamming Code Design

Project Brief

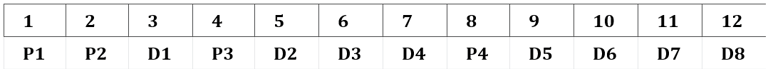

Design and simulate a hamming code having 4 parity bits (P1 P2 P3 P4) and 8 data bits (D1 D2 D3 D4 D5 D6 D7 D8) using Verilog HDL in Xilinx Vivado.

The circuit should be designed to find the parity bits from original data and check bits from received data for error detection. For check bits, use parity bits of the original data and data bits of the received data.

Hints:

For parity bits

P1 = XOR of bits(3, 5, 7, 9, 11)

P2 = XOR of bits(3, 6, 7, 10, 11)

P4 = XOR of bits(5, 6, 7, 12)

P8 = XOR of bits(9, 10, 11, 12)

For check bits

C1 = XOR of bits(1, 3, 5, 7, 9, 11)

C2 = XOR of bits(2, 3, 6, 7, 10, 11)

C4 = XOR of bits(4, 5, 6, 7, 12)

C8 = XOR of bits(8, 9, 10, 11, 12)

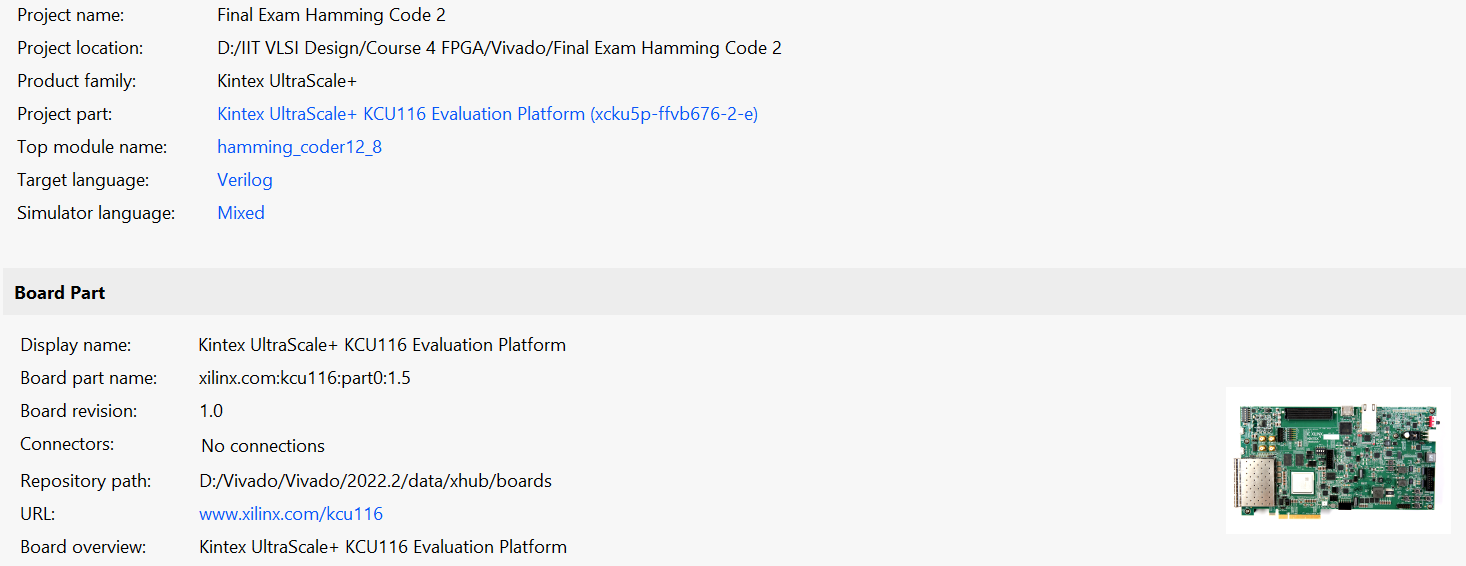

Board Part

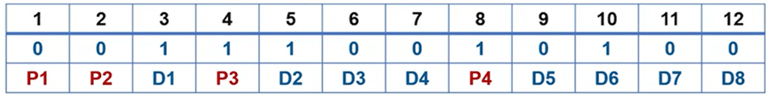

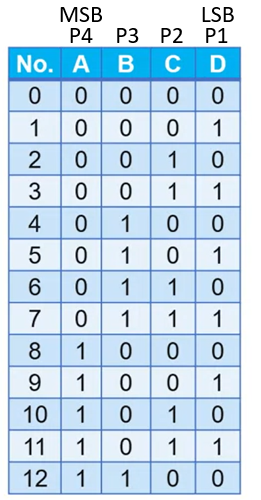

Step 1: Find the parity bits for actual data 11000100

Parity Bits:

P1=XOR of bits (3, 5, 7, 9, 11) = 0

P2=XOR of bits (3, 6, 7, 10, 11) = 0

P3=XOR of bits ( 5, 6, 7, 12) = 1

P4=XOR of bits ( 9, 10, 11, 12) = 1

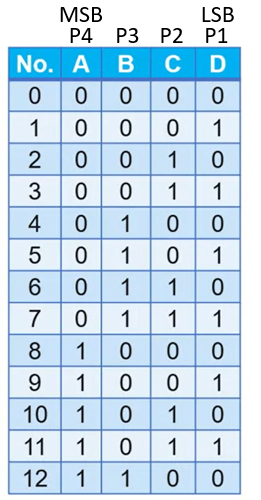

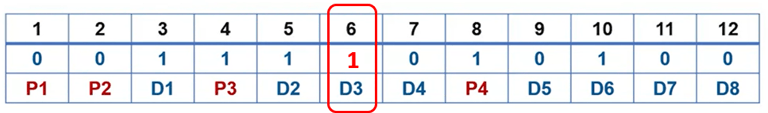

Step 2: Find the check bits of the received data 11100100

C1=XOR of bits (1, 3, 5, 7, 9, 11) = 0

C2=XOR of bits (2, 3, 6, 7, 10, 11) = 1

C3=XOR of bits ( 4, 5, 6, 7, 12) = 1

C4=XOR of bits ( 8, 9, 10, 11, 12) = 0

Bit 6 is error

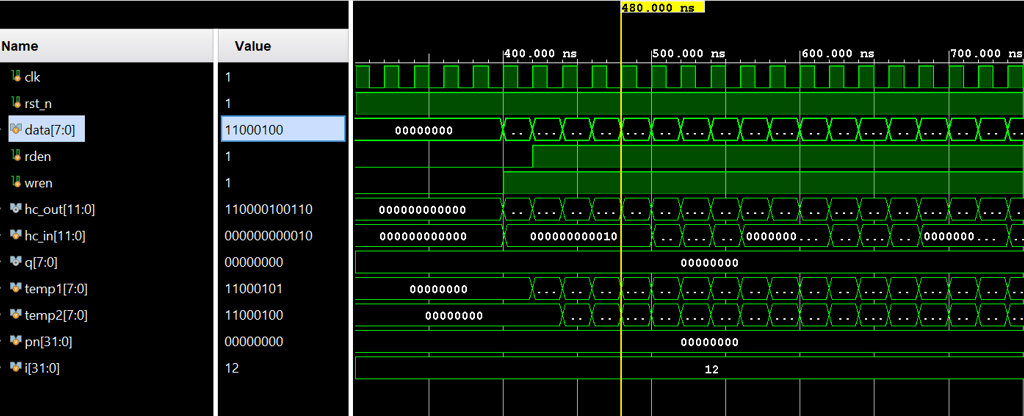

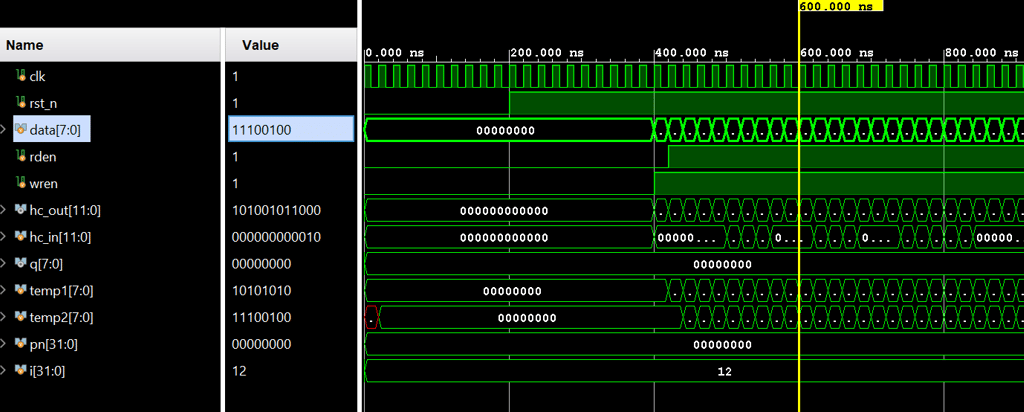

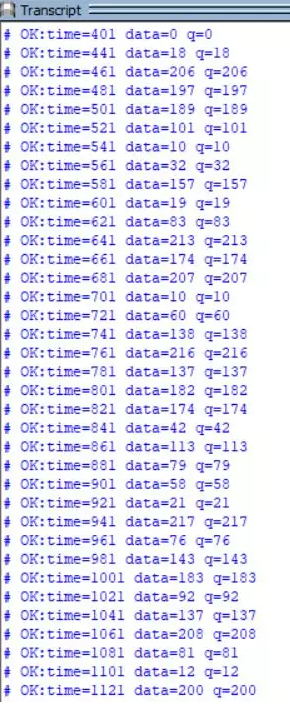

Step 2: Simulation results

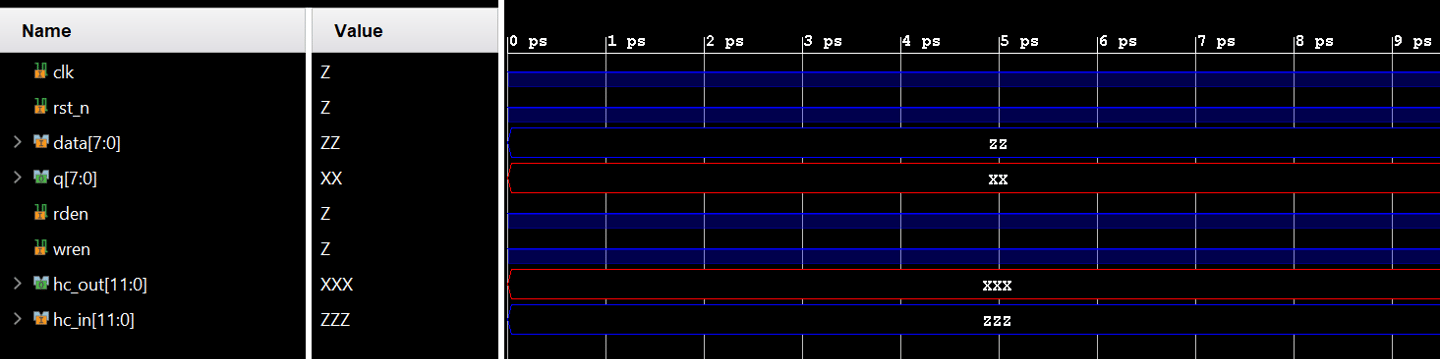

Behavioral Simulation Results

Post Synthesis Simulation Waveforms

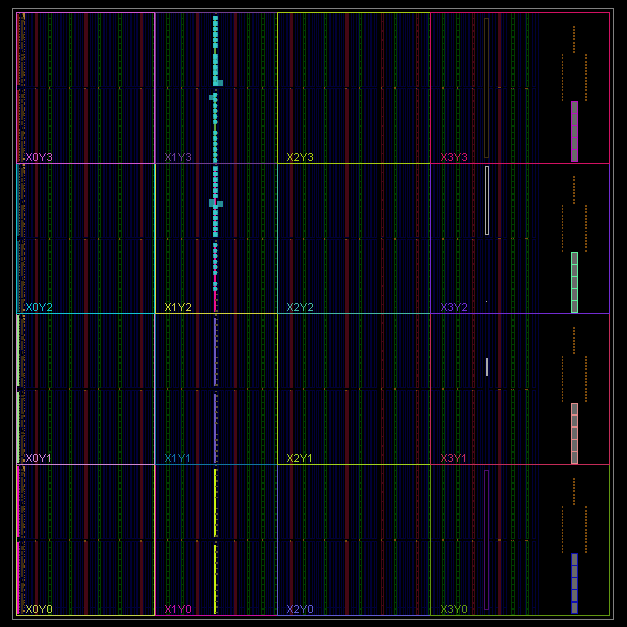

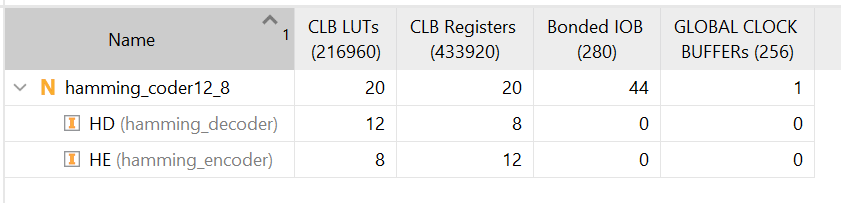

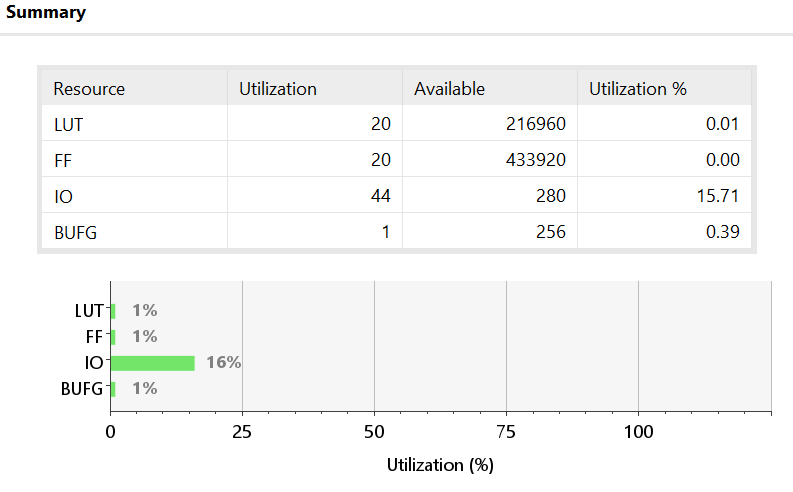

Resource Utilization Report

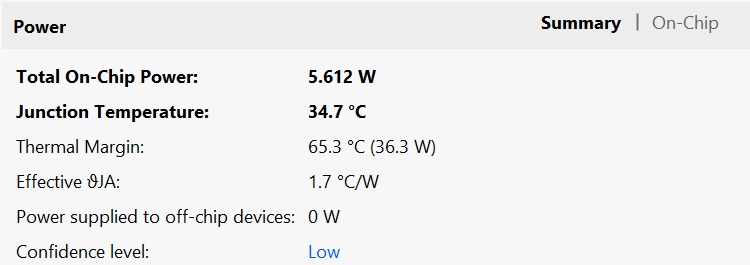

Power Consumption Report

Copyright 1986-2022 Xilinx, Inc. All Rights Reserved.

-------------------------------------------------------------------------------------------------------------------------------------------------------------------------

| Tool Version : Vivado v.2022.2 (win64) Build 3671981 Fri Oct 14 05:00:03 MDT 2022

| Date : Tue May 30 17:30:39 2023

| Host : LAPTOP-MJ3N2K2C running 64-bit major release (build 9200)

| Command : report_power -file hamming_coder12_8_power_routed.rpt -pb hamming_coder12_8_power_summary_routed.pb -rpx hamming_coder12_8_power_routed.rpx

| Design : hamming_coder12_8

| Device : xcku5p-ffvb676-2-e

| Design State : routed

| Grade : extended

| Process : typical

| Characterization : Production

-------------------------------------------------------------------------------------------------------------------------------------------------------------------------

Power Report

Table of Contents

-----------------

1. Summary

1.1 On-Chip Components

1.2 Power Supply Summary

1.3 Confidence Level

2. Settings

2.1 Environment

2.2 Clock Constraints

3. Detailed Reports

3.1 By Hierarchy

1. Summary

----------

+--------------------------+--------------+

| Total On-Chip Power (W) | 5.612 |

| Design Power Budget (W) | Unspecified* |

| Power Budget Margin (W) | NA |

| Dynamic (W) | 5.115 |

| Device Static (W) | 0.497 |

| Effective TJA (C/W) | 1.7 |

| Max Ambient (C) | 90.3 |

| Junction Temperature (C) | 34.7 |

| Confidence Level | Low |

| Setting File | --- |

| Simulation Activity File | --- |

| Design Nets Matched | NA |

+--------------------------+--------------+

* Specify Design Power Budget using, set_operating_conditions -design_power_budget <value in Watts>

1.1 On-Chip Components

----------------------

+----------------+-----------+----------+-----------+-----------------+

| On-Chip | Power (W) | Used | Available | Utilization (%) |

+----------------+-----------+----------+-----------+-----------------+

| CLB Logic | 0.119 | 48 | --- | --- |

| LUT as Logic | 0.110 | 19 | 216960 | <0.01 |

| Register | 0.008 | 20 | 433920 | <0.01 |

| BUFG | <0.001 | 1 | 32 | 3.13 |

| Others | 0.000 | 3 | --- | --- |

| Signals | 0.173 | 49 | --- | --- |

| I/O | 4.824 | 44 | 280 | 15.71 |

| Static Power | 0.497 | | | |

| Total | 5.612 | | | |

+----------------+-----------+----------+-----------+-----------------+

1.2 Power Supply Summary

------------------------

+------------+-------------+-----------+-------------+------------+-------------+-------------+------------+

| Source | Voltage (V) | Total (A) | Dynamic (A) | Static (A) | Powerup (A) | Budget (A) | Margin (A) |

+------------+-------------+-----------+-------------+------------+-------------+-------------+------------+

| Vccint | 0.850 | 0.602 | 0.405 | 0.197 | NA | Unspecified | NA |

| Vccint_io | 0.850 | 0.037 | 0.000 | 0.037 | NA | Unspecified | NA |

| Vccbram | 0.850 | 0.003 | 0.000 | 0.003 | NA | Unspecified | NA |

| Vccaux | 1.800 | 0.125 | 0.000 | 0.125 | NA | Unspecified | NA |

| Vccaux_io | 1.800 | 0.647 | 0.615 | 0.031 | NA | Unspecified | NA |

| Vcco33 | 3.300 | 0.000 | 0.000 | 0.000 | NA | Unspecified | NA |

| Vcco25 | 2.500 | 0.000 | 0.000 | 0.000 | NA | Unspecified | NA |

| Vcco18 | 1.800 | 2.035 | 2.035 | 0.000 | NA | Unspecified | NA |

| Vcco15 | 1.500 | 0.000 | 0.000 | 0.000 | NA | Unspecified | NA |

| Vcco135 | 1.350 | 0.000 | 0.000 | 0.000 | NA | Unspecified | NA |

| Vcco12 | 1.200 | 0.000 | 0.000 | 0.000 | NA | Unspecified | NA |

| Vcco10 | 1.000 | 0.000 | 0.000 | 0.000 | NA | Unspecified | NA |

| Vccadc | 1.800 | 0.008 | 0.000 | 0.008 | NA | Unspecified | NA |

| MGTYAVcc | 0.900 | 0.000 | 0.000 | 0.000 | NA | Unspecified | NA |

| MGTYAVtt | 1.200 | 0.000 | 0.000 | 0.000 | NA | Unspecified | NA |

| MGTYVccaux | 1.800 | 0.000 | 0.000 | 0.000 | NA | Unspecified | NA |

+------------+-------------+-----------+-------------+------------+-------------+-------------+------------+

1.3 Confidence Level

--------------------

+-----------------------------+------------+--------------------------------------------------------+--------------------------------------------------------------------------------------------------------------------+

| User Input Data | Confidence | Details | Action |

+-----------------------------+------------+--------------------------------------------------------+--------------------------------------------------------------------------------------------------------------------+

| Design implementation state | High | Design is routed | |

| Clock nodes activity | Low | User specified less than 75% of clocks | Provide missing clock activity with a constraint file, simulation results or by editing the "By Clock Domain" view |

| I/O nodes activity | Low | More than 75% of inputs are missing user specification | Provide missing input activity with simulation results or by editing the "By Resource Type -> I/Os" view |

| Internal nodes activity | Medium | User specified less than 25% of internal nodes | Provide missing internal nodes activity with simulation results or by editing the "By Resource Type" views |

| Device models | High | Device models are Production | |

| | | | |

| Overall confidence level | Low | | |

+-----------------------------+------------+--------------------------------------------------------+--------------------------------------------------------------------------------------------------------------------+

2. Settings

-----------

2.1 Environment

---------------

+-----------------------+--------------------------+

| Ambient Temp (C) | 25.0 |

| ThetaJA (C/W) | 1.7 |

| Airflow (LFM) | 250 |

| Heat Sink | medium (Medium Profile) |

| ThetaSA (C/W) | 2.8 |

| Board Selection | medium (10"x10") |

| # of Board Layers | 12to15 (12 to 15 Layers) |

| Board Temperature (C) | 25.0 |

+-----------------------+--------------------------+

2.2 Clock Constraints

---------------------

+-------+--------+-----------------+

| Clock | Domain | Constraint (ns) |

+-------+--------+-----------------+

3. Detailed Reports

-------------------

3.1 By Hierarchy

----------------

+-----------------------+-----------+

| Name | Power (W) |

+-----------------------+-----------+

| hamming_coder12_8 | 5.115 |

| HD | 0.165 |

| HE | 0.056 |

| clk_IBUF_inst | 0.004 |

| data_IBUF[0]_inst | 0.007 |

| data_IBUF[1]_inst | 0.008 |

| data_IBUF[2]_inst | 0.007 |

| data_IBUF[3]_inst | 0.008 |

| data_IBUF[4]_inst | 0.008 |

| data_IBUF[5]_inst | 0.008 |

| data_IBUF[6]_inst | 0.009 |

| data_IBUF[7]_inst | 0.008 |

| hc_in_IBUF[0]_inst | 0.007 |

| hc_in_IBUF[10]_inst | 0.007 |

| hc_in_IBUF[11]_inst | 0.008 |

| hc_in_IBUF[1]_inst | 0.006 |

| hc_in_IBUF[2]_inst | 0.007 |

| hc_in_IBUF[3]_inst | 0.006 |

| hc_in_IBUF[4]_inst | 0.006 |

| hc_in_IBUF[5]_inst | 0.006 |

| hc_in_IBUF[6]_inst | 0.006 |

| hc_in_IBUF[7]_inst | 0.005 |

| hc_in_IBUF[8]_inst | 0.006 |

| hc_in_IBUF[9]_inst | 0.006 |

| rden_IBUF_inst | 0.012 |

| wren_IBUF_inst | 0.009 |

+-----------------------+-----------+

Appendix

SystemVerilog

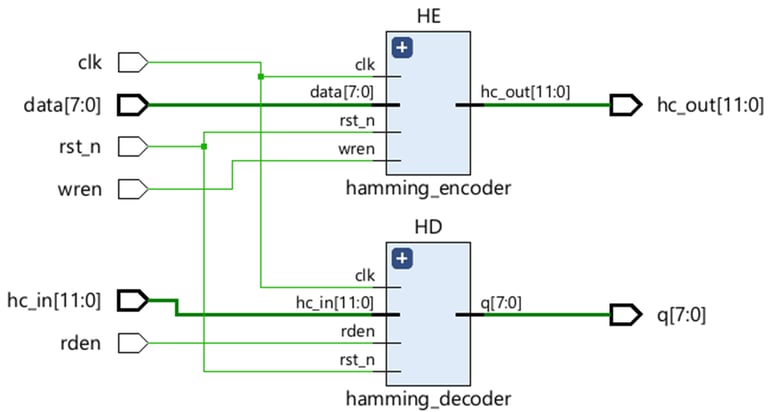

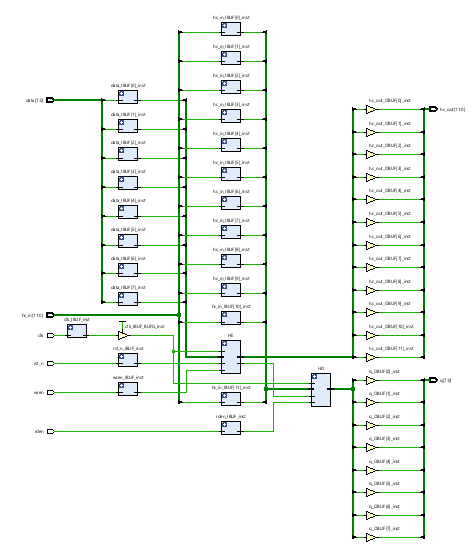

Hamming code design:

module hamming_coder12_8 (clk,rst_n, data, q, rden, wren, hc_out, hc_in);

input clk;

input rst_n;

input [7:0] data;

output reg [7:0] q;

input rden;

input wren;

output reg [11:0] hc_out;

input [11:0] hc_in;

hamming_encoder HE(

.clk(clk),

.rst_n(rst_n),

.wren(wren),

.data(data),

.hc_out(hc_out)

);

hamming_decoder HD(

.clk(clk),

.rst_n(rst_n),

.rden(rden),

.q(q),

.hc_in(hc_in)

);

endmodule

module hamming_encoder (clk,rst_n, wren, data, hc_out);

input clk;

input rst_n;

input wren;

input [7:0] data;

output reg [11:0] hc_out;

wire p0, p1, p2, p3;

assign p0 = data[0]^data[1]^data[3]^data[4]^data[6];

assign p1 = data[0]^data[2]^data[3]^data[5]^data[6];

assign p2 = data[1]^data[2]^data[3]^data[7];

assign p3 = data[4]^data[5]^data[6]^data[7];

always @ (posedge clk or negedge rst_n) begin

if(!rst_n)

hc_out <= 0;

else if(wren)

hc_out <= {data[7:4],p3,data[3:1],p2,data[0],p1,p0};

else

hc_out<=0;

end

endmodule

module hamming_decoder (clk,rst_n, rden, q, hc_in);

input clk;

input rst_n;

input rden;

output reg [7:0] q;

input [11:0] hc_in;

wire c0, c1, c2, c3;

assign c0 = hc_in[10]^hc_in[8]^hc_in[6]^hc_in[4]^hc_in[2]^hc_in[0];

assign c1 = hc_in[10]^hc_in[9]^hc_in[6]^hc_in[5]^hc_in[2]^hc_in[1];

assign c2 = hc_in[11]^hc_in[6]^hc_in[5]^hc_in[4]^hc_in[3];

assign c3 = hc_in[11]^hc_in[10]^hc_in[9]^hc_in[8]^hc_in[7];

always @ (posedge clk or negedge rst_n) begin

if(!rst_n)

q <= 0;

else if(rden)

case ({c3, c2,c1,c0})

4'b0000: q <= {hc_in[11:8], hc_in[6:4], hc_in[2]};

4'b0001: q <= {hc_in[11:8], hc_in[6:4], hc_in[2]};

4'b0010: q <= {hc_in[11:8], hc_in[6:4], hc_in[2]};

4'b0011: q <= {hc_in[11:8], hc_in[6:4], ~hc_in[2]};

4'b0100: q <= {hc_in[11:8], hc_in[6:4], hc_in[2]};

4'b0101: q <= {hc_in[11:8], hc_in[6:5], ~hc_in[4],hc_in[2]};

4'b0110: q <= {hc_in[11:8], hc_in[6], ~hc_in[5],hc_in[4],hc_in[2]};

4'b0111: q <= {hc_in[11:8], ~hc_in[6], hc_in[5],hc_in[4],hc_in[2]};

4'b1000: q <= {hc_in[11:8], hc_in[6], hc_in[5],hc_in[4],hc_in[2]};

4'b1001: q <= {hc_in[11:9], ~hc_in[8],hc_in[6:4],hc_in[2]};

4'b1010: q <= {hc_in[11:10], ~hc_in[9],hc_in[8],hc_in[6:4],hc_in[2]};

4'b1011: q <= {hc_in[11], ~hc_in[10],hc_in[9],hc_in[8],hc_in[6:4],hc_in[2]};

4'b1100: q <= {~hc_in[11], hc_in[10],hc_in[9],hc_in[8],hc_in[6:4],hc_in[2]};

default: q <= 0;

endcase

else

q <= 0;

end

endmodule

Hamming code Test Bench:

module hamming_coder12_8_tb;

reg clk;

reg rst_n;

reg [7:0] data;

reg rden, wren;

wire [11:0] hc_out;

reg [11:0] hc_in;

wire [7:0] q;

reg [7:0] temp1, temp2;

hamming_coder12_8 DUT(

.clk(clk),

.rst_n(rst_n),

.wren(wren),

.data(data),

.q(q),

.rden(rden),

.hc_in(hc_in),

.hc_out(hc_out)

);

integer pn, i;

initial begin

pn=0;

hc_in=0;

forever begin

@(posedge clk)

pn={$random} %12;

#1

for (i=0; i<12;i=i+1) begin

if (i!=pn)

hc_in[1] = hc_out[i];

else

hc_in[1] = ~hc_out[i];

end

end

end

always @ (posedge clk)

begin

temp1<= data;

temp2 <= temp1;

end

always @ (*)

begin

if(wren) begin

#1

if (temp2==q)

$display("OK: time=%0t data=%0d q=%0d", $time, temp2, q);

else

$error("ERROR: time=%0t data=%0d q=%0d", $time, temp2, q);

end

end

initial begin

clk = 1;

rst_n=0;

data= 0;

rden = 0;

wren = 0;

#200

@(posedge clk)

rst_n=1;

#200

forever begin

@(posedge clk)

wren = 1;

data = {$random}%9'b10000_0000;

@(posedge clk)

wren = 1;

data = {$random}%9'b10000_0000;

rden = 1;

end

end

always#10 clk = ~clk;

initial #5000 $stop;

endmodule